# Chapter 6

# Synchronous Sequential Machines

A block diagram of a sequential circuit was shown in the introduction of Chapter 5. That chapter concentrated on one part of such a circuit: the memory devices, or flip-flops. Those circuits in which state transitions are controlled, or synchronized, by a clock are said to be *clocked*, or *synchronous*, sequential circuits. Other sequential circuits exist, called *asynchronous* circuits, in which state transitions are not synchronized by a clock. These are less common, although they do have important applications. We will postpone the discussion of such circuits to Chapter 7.1

A number of tools are used to describe the behavior of sequential logic circuits and to analyze and design them. We will introduce and develop such tools in this chapter. Included are formal procedures for the design of synchronous machines. Finally, we will concentrate on one class of such circuits and their design: circuits called *counters*.

### 1 BASIC CONCEPTS

The generic description of a problem requiring the design of a synchronous sequential logic circuit can be given as follows.

Design a digital circuit whose outputs are to take on specific values after a specific sequence of inputs has taken place.

Such a problem statement is very broad. What is clear is that

• There are to be certain sequences of inputs to the circuit.

<sup>&</sup>lt;sup>1</sup>With or without adjectives to qualify it, the term *machine* is often used to designate a sequential circuit, as in the title of this chapter. Because such circuits can have only a finite number of states, they have also been called *finite-state machines*. Since finiteness is all that is possible in the physical world, this adjective is often dropped and the circuits in question are simply called *state machines*. "Machine" normally has the connotation of something physical. However, in the present usage, the term refers to an abstract entity described by mathematical, graphical, or tabular means, as we will describe in this chapter.

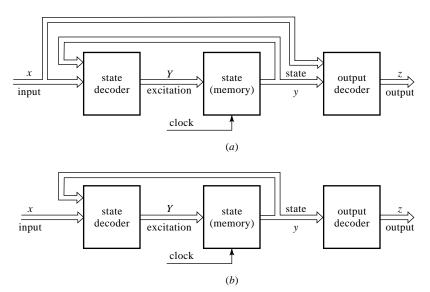

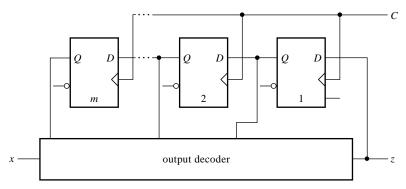

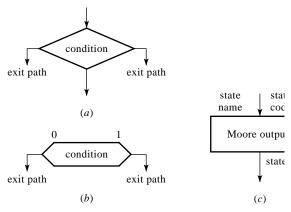

**Figure 1** Models of Mealy and Moore machines.

- Different sequences of past inputs will constitute different states or conditions of the circuit.

- Specific outputs result only following a specified input sequence.

The general description does not specify whether the output will depend just on the past inputs or on the latest input as well.

These two possibilities lead to different structures, first explored in the mid-1950s by two people named Mealy and Moore. As mentioned in Chapter 5, in *Mealy machines* the outputs depend both on the present state (resulting from past inputs) and on the current input. The outputs in *Moore machines* depend only on the present state (resulting from past inputs). Attention will be devoted to both types.

Block diagrams of both Mealy and Moore models of sequential machines were given in Chapter 5, Figure 1. Somewhat refined versions are shown in Figure 1 here. The open arrowheads imply multiple variables. For example, input x stands for the set of variables  $\{x_1, x_2, \ldots, x_n\}$ . The combinational part of the circuit is broken down into two separate parts: the *state decoder* and the *output decoder*. The state decoders in both models accept as inputs both primary (external) inputs and the present state. In the Moore machine, however, the output decoder accepts only the present state to yield outputs. In the simplest case, there is no output decoder at all; the states themselves are the outputs. In a given machine, there may be some outputs that are Moore-type outputs and others that aren't. Such a machine must be classified as a *Mealy machine*, since at least *some* of its outputs depend not only on the state, but also on the inputs. Thus, the Mealy machine is the more general (and more common) type.

The behavior of synchronous sequential logic circuits can be described in a number of ways. At any given clock pulse, the state of the circuit is the *present state*. Signals present at the input terminals at that time are the *inputs*. This

combination of present state and input results in two things: a transition to the *next state* and an *output*. At the next clock pulse, the process is repeated, except that the present state is now what the next state was at the preceding clock pulse. It is possible to conceive of this process as never ending; that is, the "next state" is never a state that had been previously encountered. In this case, the machine would be infinite—a peculiar machine indeed. Barring such an unlikely event, somewhere along the line the next state will be a previously encountered state. After this, the machine will retrace its steps over and over; no new states will be encountered.

Several means are available for illustrating the following sequence:

present state/input  $\rightarrow$  clock pulse  $\rightarrow$  next state/output

One of these means is graphical/diagrammatic; another is tabular. A third approach utilizes a chart not unlike a flow chart describing an algorithm. All are treated in this chapter.

# **State Diagram**

The graphical/diagrammatic tool for describing sequential circuit behavior is known as a *linear graph*. For each state of the circuit, there is a corresponding node in the graph. (The circle representing the node is made large enough that the symbol for the state can be written inside.) With the machine in any one state (node in the graph), at the occurrence of a clock pulse, there will be a state transition to the next state and there will be an output, both in accordance with the problem statement. For a single-input machine, two lines emanate from each node, one each for a 0 and for a 1 input. For two input variables, four lines emanate from each node, one for each input combination: 00, 01, and so on. (How many lines will emanate from each node if the number of input variables is n?) Along each line we write the input value and the corresponding output separated by a slash. The resulting graph is called a *state diagram*.

For some state machines it is known from the statement of the problem just how many distinct states the machine has. However, in general, the number of possible states is initially unknown. To establish the state diagram, we arbitrarily choose an initial state and label it, say, A. (State names can be anything convenient.) A state is identified by unambiguously specifying how it is reached. To say, for example, that "state S is reached when the input is 1" is inadequate, because the statement does not *unambiguously* identify it: Does this 1 follow another 1? Is it the first 1 after a string of 0's? Does this 1 follow a string of two or more preceding 1's? One unambiguous specification would be: "State S is reached by the second of two input 1's after one or more 0's."

Because it is difficult to describe, in the abstract, both the state diagram and the tabular tool to be discussed next, we will continue this discussion in conjunction with an example.

Short

Even

<sup>&</sup>lt;sup>2</sup>A linear graph is a set of *nodes*, or *vertices* (drawn as circles), interconnected by a set of directed lines (or arcs), that is, lines that have an orientation indicated by an arrowhead.

<sup>&</sup>lt;sup>3</sup>Except for a trivial case that will be described shortly.

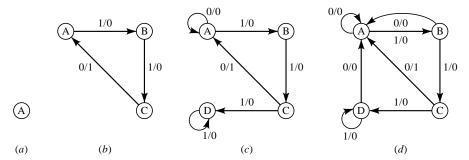

Figure 2 State diagram of sequence detector.

### **EXAMPLE 1**

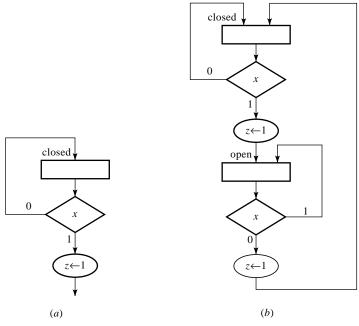

A synchronous sequential machine with a single input line x and a single output line z is to be designed. The specifications are as follows: the output is to be z=1 if and only if the specific input sequence ...0110 occurs at consecutive clock pulses; otherwise z=0. (Unless otherwise stated, the most recent bit of a sequence is the one on the right in all cases.) Suppose, for example, that an input sequence is ...0110110. The first 4 bits identified constitute an *acceptable* (that is, *output-producing*) input sequence. But the fourth bit starts another acceptable sequence that overlaps with the first. Hence, the output sequence will be ...0001001. (Confirm.) Such a machine is called a *sequence detector*.

Let's identify our initial state A as the state reached by an input x = 0 regardless of the preceding sequence of inputs. It doesn't matter if the preceding input bit is 1 or 0 for a 0 input bit to start an acceptable sequence. We start the state diagram by drawing a node labeled A. Following this, there are two possible strategies:

- We can explore the consequences (next state/output) resulting from each possible input starting in this state, and continue in this fashion with all the next states encountered along the way.

- We can assume an acceptable sequence and pursue the consequences (string of next states and outputs), adding states as needed. Then we return to each state encountered along the way to fill in the consequences of inputs that are not part of an acceptable sequence.

The second method is carried out in Figure 2. Starting from state A (reached by a 0 input), we assume an input sequence 110 to complete an acceptable sequence. The result is shown in Figure 2*b*. (Confirm that the two additional states shown must be introduced along the way. Also confirm each of the steps that follow.)

Starting at each state in Figure 2*b*, only one of the two possible inputs has been used so far. Now we fill in the other possibilities. From state A, an input of 0 leads back to state A/output 0. From state B, an input of 0 also leads back to A/output 0. But what is the next state if there is an input of 1 while the machine is in state C (which was reached by an input sequence 011)? It can't be to any of the three states reached so far (confirm this), so it must be to a new state D/output 0. The state diagram so far is shown in Figure 2*c*. Finally, from this new state, an input of 0 leads back to A/output 0 and an input of 1 leads back to D/output 0. The final diagram is shown in Figure 2*d*.

Study the last diagram. A is the state reached by the first bit in an acceptable sequence. The sequence is aborted if the next input is also 0. Now it is this last 0 that starts an acceptable sequence. Any number of additional inputs of 0 lead to the same result: the latest 0 becomes the first bit of an acceptable sequence. The last state, D, is an acceptable-sequence spoiler; it is reached by an input of 1 following a sequence ...011.

Notice in Figure 2 that all but one of the arcs in the graph are labeled with an output of 0. A lot of clutter could be avoided if we adopt the convention that only outputs of 1 will be shown explicitly. When the output associated with a particular arc is 0 (or 00, 000, etc. for more output variables), henceforth it will not be shown explicitly on the state diagram.

In constructing a state diagram, there are generally two major decision points:

- **1.** Choosing the initial state

- **2.** When in a particular state, deciding whether the transition resulting from a particular input is to an existing state or to a new state not yet identified

In some (not all) sequential machines there is a specific *reset* state; the machine must be in this state at the starting time. In such cases, the initial state is predetermined. When there is no reset state, the initial state is chosen arbitrarily, as in the preceding example. Although the problem statement might guide the choice of initial state, different designers might choose different initial states.<sup>4</sup> No problem. Assuming there are no mistakes, two state diagrams constructed with different initial states will be *isomorphic;* that is, they will become identical by an appropriate interchange of state names.<sup>5</sup>

As for the second decision point, a transition to a new state rather than to an existing state will result in more states in the state diagram. Eventually, a circuit must be implemented. Generally speaking, more states mean more flipflops, though not proportionately more. A circuit with n flip-flops, for example, will have  $2^n$  states. Conversely, then, eight  $(2^3)$  states will require three flipflops. But even as few as five states will still require three flip-flops. Thus, if a state diagram has five states already, increasing the number of states to as many as eight will not increase the number of flip-flops needed. Thus, introducing more states in a state diagram may simply mean introducing redundancies; these might be removable later.

Although in the preceding example we constructed a state diagram that describes all the state transitions of the desired machine, we still did not complete a design. Before tackling that task, we turn to the tabular tool for describing the behavior of a sequential machine.<sup>6</sup>

Short

Even

<sup>&</sup>lt;sup>4</sup>They may also give the states different names, the placement of the nodes might be different, and the curvatures of the lines joining the nodes might be different. All of these are trivial matters.

<sup>&</sup>lt;sup>5</sup>This assumes that no extra states are introduced, as will be described shortly.

<sup>&</sup>lt;sup>6</sup>Suppose we reconsider the statement "State S is reached when the input is 1." The state diagram will then consist of just two states: S is the state reached by an input 1 and, say, T is reached by an input 0. Any other 0 inputs while in state T will return the machine to state T. A 1 input will send the machine back to state S. Any other 1 inputs will keep the machine in state S. Construct a state diagram for yourself. This is a trivial "machine."

|    | NS,Z  |       |  |  |  |  |  |

|----|-------|-------|--|--|--|--|--|

| PS | x = 0 | x = 1 |  |  |  |  |  |

| A  | A,0   | B,0   |  |  |  |  |  |

| В  | A,0   | C,0   |  |  |  |  |  |

| C  | A,1   | D,0   |  |  |  |  |  |

| D  | A.0   | D.0   |  |  |  |  |  |

N TO

**Figure 3** State table of sequence detector in Example 1 obtained from its state diagram.

# **State Table**

A table can be described by its row headings (or names) and its column headings. Its entries occur at the intersections of the rows and columns. To describe the operation of a synchronous machine, it is customary to choose the row headings as the present states and the column headings as the inputs.

Since two outcomes (next state, output) result from an input to the circuit when the circuit is in a particular state, it is conceivable to construct two separate tables. The entries in one of these would be the circuit outputs—hence it is called the *output table*. The entries in the other table would be the next states. Since the table is intended to show transitions from a present state to a next state, it might be tempting to call this table a state transition table. But in the preceding chapter, state transition table was the name given to the table that specifies the next state resulting from inputs to a flip-flop for each present state of the flip-flop. So we use a different name; it is called simply a *state table*. In the present usage, the circuit is not limited to a single flip-flop but encompasses an entire machine.

Remember from Figure 1*b* that the output of a Moore machine depends only on the present state. For such a machine, there will be only one output combination for each input combination; hence, a separate output table makes more sense. For a Mealy machine, on the other hand, we will combine the state and output tables into a single table in which the entries are both the next states and the resulting outputs, separated by a comma.<sup>7</sup> This will be illustrated for Example 1, whose state diagram was obtained in Figure 2. (Of course, once this table is available, it is always possible to separate the next-state part and the output part into two separate tables if there is a reason for doing so.)

# **Constructing a State Table from a State Diagram**

Once a state diagram is available, the corresponding state/output table is easily constructed. The state diagram in Figure 2 has four states. Hence, the corresponding state/output table will have four rows. Starting in any state, the output and the next state can be obtained from the diagram and entered in the table. The result is given in Figure 3.

**Exercise 1** Notice in Figure 2 that state A is reached from each state (including A) by an input 0 but with different outputs: 0 from states A, B, D and 1 from state C. Instead, let's suppose that state A in the state diagram of Figure 2 is

Short \_\_\_\_

Even \_\_\_

7It is also sometimes called a *flow table*.

identified as the state reached by an input 0 resulting in an output 1. Now start from Figure 2*a* and assume that a 0 input while in state A or state B leads to a new state E rather than back to A. Complete the resulting state diagram. (You don't need to take the following advice, but you won't get tangled up in crossing lines if you put A, B, and C in a row, with D under C and E under B.) Then, from the diagram, construct a state table.

Answer<sup>8</sup>

Examine states A and E in your table from Exercise 1. Both are reached by an input bit 0. Hence, starting from either state, the next states and outputs must be the same for each input bit. In this case, these two states can't be distinguished from each other. This is the basis for a definition:

Two states are said to be indistinguishable if, for each input combination, the resulting outputs and next states are the same.

Actually, the next states need not be the same—only indistinguishable, as just defined.

On this basis, states A and E are indistinguishable. If all E next states in the table are replaced by A, and row E is eliminated, the table obtained in Exercise 1 will become the same table obtained in Figure 3.

There are formal procedures for extending the concept just defined. We will pursue this generalization in the following section and discuss ways of reducing the number of rows of a state table. Consequently, in constructing a state diagram in the design of a sequential circuit, there is no great need to worry about introducing redundant states; such states can be removed subsequently. On the other hand, there is no point in needlessly extending a state table, since effort will be needed later to reduce it. When in doubt while constructing a state table, by all means introduce a new state. However, restrain yourself if you are certain that the relevant conditions have already been identified by an existing state.

### **EXAMPLE 2**

(*Note:* One of the topics treated in section 4 of Chapter 1 is the Hamming code. Review it if you need a refresher.) To an *n*-bit message, an additional *k* bits are added, making the parity of the resulting (n + k)-bit string either odd or even—our choice. In this example, let n = 3 and k = 1; let's choose odd parity. Suppose that a 4bit string is to be received; the first 3 bits constitute the message, and the fourth bit is always 0 (equivalent to a blank). If the number of 1's in the 3-bit message is odd, the parity bit is to remain 0. If the number of 1's is even, a 1 bit is to be generated

<sup>&</sup>lt;sup>8</sup>Now, only one arc of the graph with input 1 enters A (from C/output 1). Four arcs enter E (from A, B, D, and E, all with 0 in, 0 out. D is a spoiler state, entered by a string of three 1's starting at A; any further 1's while in state D will keep the state in D. An input 1 while in state E is the first 1 after one or more 0's; in that respect, an input 1 while in state E should lead to the same state as a 1 while in state A, namely, state B.

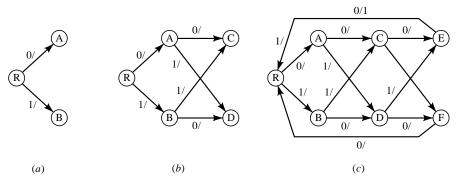

Figure 4 State diagram of parity-bit generator.

|              | N:    | S,z               |

|--------------|-------|-------------------|

| PS           | x = 0 | <i>x</i> = 1      |

| R            | A,0   | B,0               |

| Α            | C,0   | D,0               |

| В            | D,0   | C,0               |

| C            | E,0   | F,0               |

| D            | F,0   | E,0               |

| $\mathbf{E}$ | R,1   | $R,\times$        |

| E            | RΛ    | $\mathbf{P} \vee$ |

**Figure 5** State table for parity-bit generator.

and inserted in the fourth position to make the parity of the 4-bit string odd. In either case, after the fourth bit, transition is to be to a reset state, in which the machine is ready to receive the next message sequence. Such a machine is a *parity-bit generator*. Our objective is to create a state table.

The first step is to create a state diagram. The machine is to be in the reset state (say R) when the first bit arrives. The partial state diagram after the first bit is shown in Figure 4a. There cannot be a 1 output until the parity bit arrives and completes a 4-bit string whose parity is even. At each input, the parity of the input bits up to that point is either even or odd, so transition is to one of two possible next states: an even-parity state or an odd-parity state.

The partial diagram after the second message bit is shown in Figure 4b. Why is it necessary for the next state at the second input bit to be a new state rather than one of the existing odd-parity or even-parity states, A or B? (Give it some thought before you look at the footnote.<sup>9</sup>) Confirm the details of the complete diagram shown in Figure 4c; for example, show all possible input sequences by which states E and F are reached. An output of 1 occurs only upon returning to reset from state E following one of the sequences 0000, 0110, and 1100.

The next step is to construct the flow table from the state diagram. It is shown in Figure 5. The fourth input bit is never 1; so what will the output be for

<sup>&</sup>lt;sup>9</sup>If A can be reached both after a single 0 and after a string 00, for example, then the count of the number of input bits is lost. Hence, we can't tell when the third bit has arrived in order to decide whether or not to generate a 1-bit, nor can we tell when the fourth bit has arrived so as to go back to the reset state.

|    | NS,z  |              |          | $(y_1)$      | V <sub>2</sub> )+ | $y_1^+$              |       |              |                      | $y_2^+$      |              |

|----|-------|--------------|----------|--------------|-------------------|----------------------|-------|--------------|----------------------|--------------|--------------|

| PS | x = 0 | <i>x</i> = 1 | $y_1y_2$ | x = 0        | <i>x</i> = 1      | $\underline{y_1y_2}$ | x = 0 | <i>x</i> = 1 | $\underline{y_1y_2}$ | x = 0        | <i>x</i> = 1 |

| Α  | A,0   | B,0          | A→00     | 00           | 01                | 00                   | 0     | 0            | 00                   | 0            | 1            |

| В  | A,0   | C,0          | B→01     | 00           | 10                | 01                   | 0     | 1            | 01                   | 0            | 0            |

| C  | A,1   | D,0          | D→11     | 00           | 11                | 11                   | 0     | 1            | 11                   | 0            | 1            |

| D  | A,0   | D,0          | C→10     | 00           | 11                | 10                   | 0     | 1            | 10                   | 0            | 1            |

|    | (a)   |              |          | ( <i>b</i> ) |                   |                      | (c)   |              |                      | ( <i>d</i> ) |              |

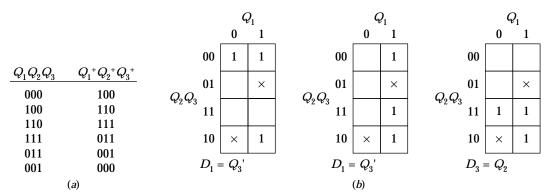

**Figure 6** State and transition tables for sequence detector.

x = 1 from states E and F? Confirm all the details of this table by reference to the state diagram.

### 2 STATE ASSIGNMENTS

The preceding section described the initial stage in the design of a Mealy-model synchronous sequential machine. From a word description of the specifications of the problem, it consists of constructing a state/output table (possibly after constructing a state diagram). During this process, it is possible that redundant states are introduced; consequently, the table might have more states than necessary to perform the desired task. Procedures for eliminating redundant states would be useful, leading to a reduced table with fewer states that is equivalent, in some sense, to the original table. Fortunately, such procedures do exist, and we will discuss them later. For the present, assume that a reduced table is available.

The state of a sequential machine at a given time is the condition in which past inputs have left it. This information is stored in the flip-flops; the state is, thus, described collectively by the outputs of the flip-flops. The next step in the design, then, is to identify the states in the table with specific flip-flop outputs. That is the subject of concern in this section. We will develop the subject by reference to the examples in the preceding section.

### **EXAMPLE 3**

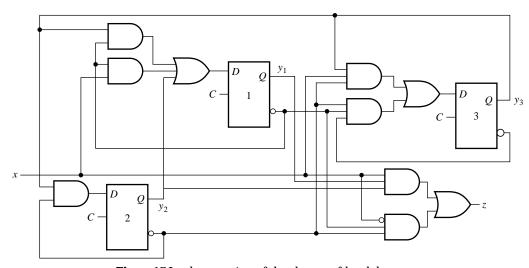

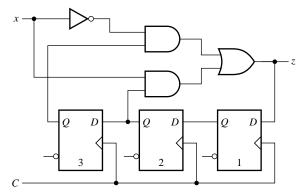

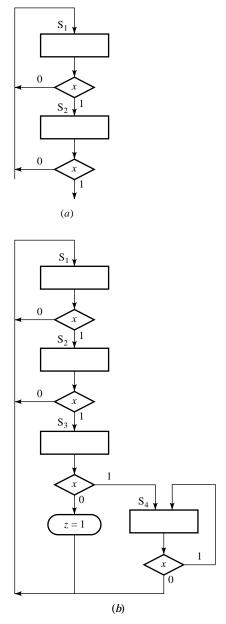

The state table derived for the sequence detector in Example 1 was given in Figure 3 and is repeated in Figure 6a. The minimum number of state variables needed for a circuit implementation of this table is  $\lceil \log_2 4 \rceil = 2$ , where  $\lceil k \rceil$  denotes the *ceiling* of k, the smallest integer not less than k. Let us designate the state variables as  $y_1$  and  $y_2$ . There are four possible combinations of values of these two variables. How should these four combinations be assigned individually to each of the four states? Before considering a general answer to that question, let us arbitrarily make the assignment shown in Figure 6b. (Let's temporarily neglect the output z and concentrate on the states.) The result is a table that, for each present combination of state-variable values and each input value, specifies the next combination of state-variable values. This is a *state-transition table*.

Note that there are two different orders: the order of listing the states in the state table (alphabetical) and the order of the combinations of state-variable values. If the assignment is made so that both orders are maintained, there is no prob-

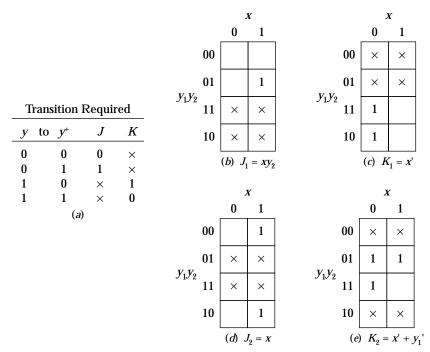

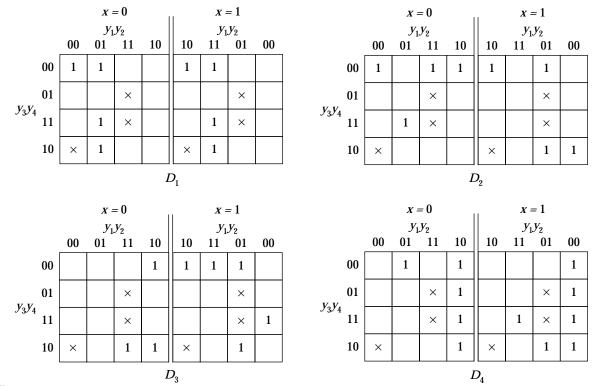

**Figure 7** Excitation maps for the sequence detector.

lem. For any other assignment, either one or the other order can be maintained, but not both. It is much more convenient to maintain the order of the value combinations than the order of the state names, since the former is directly transferable to a logical map. This is what has been done in Figure 6*b*; states C and D are out of alphabetical order, but the value combinations are in logic map order.

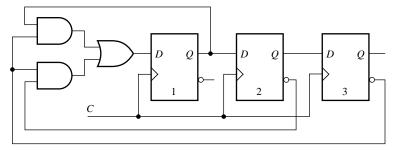

For simplicity, the transition table in Figure 6b is separated into two tables in Figures 6c and 6d, one for each state variable. If we were to implement the design with D flip-flops, each of these tables would represent the excitation map for one of the flip-flops; for a D flip-flop, the present input (excitation) is the same as the next state. Just for pedagogical reasons let's implement it with JK flip-flops instead.  $^{10}$

The first requirement is to determine logic maps for excitations J and K for each flip-flop. For this we use the excitation requirements for JK flip-flops given in Chapter 5, Figure 17, and repeated here in Figure 7a. For each flip-flop, this table gives the required values of J and K for each transition from a present-state value to a next-state value. In each case, J and K are to be obtained as the output of a combinational circuit whose inputs are the circuit input x and present states  $y_1$  and  $y_2$ . This requires combining the transitions from present to next state in Figures 6c and 6d with the transition requirements table in Figure 7a. Thus, from state  $y_1y_2 = 11$  and x = 1, transition is to  $y_1^+$   $y_2^+ = 11$  from Figures 6c and 6d. That is, for both  $y_1$  and  $y_2$ , transition is from 1 to 1 for x = 1. But from Figure 7a, the requirements for a 1 to 1 transition is

$<sup>^{10}</sup>$ Only one combinational logic circuit is needed for the excitation when implemention is with D flip-flops. With JK flop-flops, two circuits are needed, one each for J and K. It is, of course, possible that the circuit required with a D flip-flop is more complex; nevertheless, with present-day implementations with PLDs, it is usually preferable to use D flip-flops. Furthermore, JK flip-flops require more chip area in ASIC technology.

**Figure 8** Implementation of the sequence detector.

$J = \times$  and K = 0. These constitute the content of one square in the logic maps for each J and K. The completed logic maps are shown in Figures 7b to 7e. (Confirm each of them and confirm the expressions for J and K given under the maps.)

To complete the implementation, an expression for the output function must be obtained. From the flow table in Figure 6a the output is 1 for exactly one state (state C) and one input (x = 0). Since C has the assignment  $y_1y_2 = 10$ , the expression for the output function is

$$z = x' y_1 y_2'$$

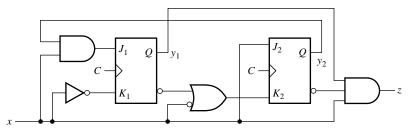

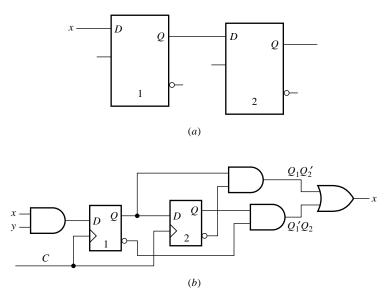

The complete implementation is shown in Figure 8. (Confirm it all.)

# Analysis

Once a sequential circuit has been designed and a logic diagram constructed, how can we tell that errors have not been made and that the circuit outputs actually satisfy the original specifications? As discussed in relation to combinational circuits in Chapter 3, a process called *verification* is carried out. This involves making measurements (of voltage, say) at appropriate points in any circuit (not just logic circuits) to verify that the actual values are what they are supposed to be theoretically.

Again, as discussed in Chapter 3, there is no point in physically implementing the circuit before verification. Once a paper (or software-generated) sequential circuit has been obtained, one can *analyze* the circuit at various points to verify that the logic values at these points are indeed the values required by the design specs. Compared with the process of design, logic-circuit analysis is rather trivial. One starts at any point in the circuit (gate or circuit outputs, or MUX, flip-flop, or register inputs) and determines logic expressions for these variables. This is repeated until expressions for all outputs are obtained. Then one inserts all possible input values into these expressions. The values obtained are then compared with what they are supposed to be.

As an example, look back at the sequence-detector design in Figure 8. Carry out an analysis of the circuit and obtain expressions for the Js and K's and the output z. (Don't peek at Figure 9 until you have completed it.) The lines on the time axis in Figure 9 represent the rising edge of the clock signal. Using these expressions and the transition table of JK flip-flops, and assuming the input sequence shown on the first line, the values of the other variables are determined column by column. Note that, when x = 0, the values of the Js and Ks do not depend on the states of the flip-flops; hence, the next states in the

|                  |             |   |   |   |   |   |   |   |   |   | Ti | me |

|------------------|-------------|---|---|---|---|---|---|---|---|---|----|----|

|                  |             | + | - | - | - | - | - | - |   |   | -  | +  |

| X                |             | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1  | 1  |

| $\overline{J_1}$ | $xy_2$      | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |   |    |    |

| $\overline{K_1}$ | X'          | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 |   |    |    |

| $J_2$            | X           | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |   |    |    |

| $K_2$            | $(xy_1)'$   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |   |    |    |

| $y_1^+$          |             | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |   |    |    |

| $y_2^+$          |             | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |   |    |    |

| Z                | $x'y_1y_2'$ | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |   |    |    |

**Figure 9** Timing table for the implementation in Figure 8.

first column are based only on x = 0. When x = 1, the values of  $J_1$  and  $K_2$  do depend on the states (not the next states in the same column but the states in the previous column). Verify the remaining columns and complete the last three columns in Figure 9. Verify that the outputs satisfy the specifications.

**Exercise 2** Using the information in Figure 9, choose an appropriate scale and draw a timing diagram that includes the circuit input, the flip-flop inputs, the next states, and the circuit output.

# **Rules of Thumb for Assigning States**

A number of loose ends in the preceding development remain to be explored. The first is the simple observation that, when a transition table is obtained after a state assignment is made, as in Figure 6b, it is not essential to rewrite it in the form of the individual state variable transition tables, as was done in Figures 6c and 6d, before constructing the excitation maps. Instead, for each input value, concentrate on the column corresponding to one of the state variables, say  $y_1$ , mentally blocking the others from your perception, and construct the maps directly from the general transition table. Practice doing that for Figure 6b.

A more important consideration is the following. Given a state table having k states, the number of state variables needed to implement it is  $n = \lceil \log_2 k \rceil$ . An immediate decision is needed as to which of the  $2^n$  combinations of state-variable values should be assigned to each of the k states. For a nontrivial number of states, many different possibilities exist for this assignment.

**Exercise 3** The state table for the sequence detector in Example 1 was given in Figure 6a. The implementation of the circuit using the assignment in Figure 6b was given in Figure 8. Instead, use the following assignment and find an implementation for the circuit: A: 00, B: 01, C: 11, D: 10. Compare the number of gates with the number in Figure 8.

Answer<sup>11</sup>

<sup>&</sup>lt;sup>11</sup>One more gate than the number in Figure 8.

- 1. Two present states should be assigned adjacent codes if they have the same next state for:

- a. Each input combination

- b. Different input combinations, if the next state can also be given adjacent assignments

- c. Some input combinations, but not necessarily all

- 2. For all inputs, codes assigned to the next states for each present state should be adjacent.

- 3. Assignments should simplify the output function.

Figure 10 State assignment rules.

In general, the choice of assignment will influence the implementation. Different assignments lead to different maps of flip-flop excitation and output and, hence, to different expressions for excitation functions and output functions. Unfortunately, there is no general theory on assignments—and so no algorithm—that will result in simplicity of implementation. Experience is the only guide to making a state assignment.

General models of sequential circuits were given in Figure 1. Although the actual circuit in Figure 8 is quite simple, it illustrates the Mealy model well. The nonsequential part of the circuit consists of two classes: the combinational circuit that implements the excitations and the one that implements the output, as expected. Once state reduction has been carried out (until you learn how, you'll have to subcontract it out), the extent of the memory (the number of flip-flops) is fixed. Economy of implementation, then, is a matter of reducing the number of IC packages (and gates) in either the state decoder, the output decoder, or both.

Recall that the number of prime implicants and the number of literals in a prime implicant can be reduced when there are many adjacent minterms. Hence, it comes down to this: How do we choose state assignments so as to achieve a large number of adjacencies? Not much in the way of generalities can be deduced from an examination of Example 3. However, on the basis of a great deal of experience, some heuristic "rules" have been formulated as guides in making a state assignment for the case of a single input. Figure 10 lists a number of such rules, in priority order.

For a given state table, it is unlikely that all the adjacencies specified by these rules can be achieved. When there is a conflict, the higher-priority rules take precedence. Even if the rules can be fully implemented, they do not guarantee an optimal assignment. That is, the rules do not constitute an optimal algorithm.

Furthermore, they do not necessarily lead to a unique assignment; it may be possible for the required adjacencies to be achieved by different assignments. Even so, the rules will reduce the number of alternatives that must be checked. Finally, even for the same assignment, the number of logic gates using JK flipflops might be different from the number using D or other flip-flops. Notwithstanding all that, using these rules as a guide is reasonable.

### **EXAMPLE 4**

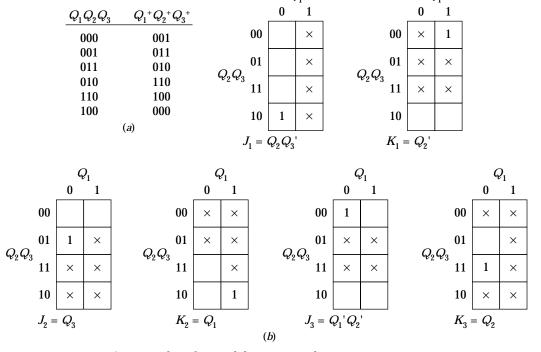

An application of the assignment rules in the implementation of a sequential ma- \_\_\_\_ Short chine is illustrated in the state table shown in Figure 11a. Since there are seven states,  $\_$  Even

| NS,z         |         |              | _    |              |          | y | <b>'</b> 1 |

|--------------|---------|--------------|------|--------------|----------|---|------------|

| PS           | x = 0   | <i>x</i> = 1 |      |              |          | 0 | 1          |

| A            | B,1     | B,0          | Rule | Adjacencies  | 00       | Α | E          |

| В            | C,0     | D,1          |      |              | 01       |   | T.         |

| C            | E,1     | F,0          | 1a   | AG           | 01       | G | F          |

| D            | F,0     | E,1          | 1b   | CD if EF     | $y_2y_3$ |   | В          |

| $\mathbf{E}$ | G,0     | A,0          |      | EF if AG     | 11       |   | D          |

| F            | A,0     | G,0          | 2    | CD, EF, AG   | 10       | С | D          |

| G            | B,0 B,0 |              | 3    | AC, BD       | 10       |   | ש          |

|              | (a)     |              |      | ( <i>b</i> ) |          | ( | c)         |

Figure 11 Example state table, adjacencies, and assignment map.

the circuit will need  $\lceil \log_2 7 \rceil = 3$  flip-flops. The adjacencies of states called for by the adjacency rules are shown in Figure 11*b*. (Don't fail to confirm these.) It is now a problem of determining a state assignment so that as many as possible of these adjacencies is achieved. To help in this process, an assignment map can be created, as shown in Figure 11*c*. This is a map whose coordinates are the three state variables. Each square in the map corresponds to a combination of state variable values.

The placement of the states in the map is initiated by deciding on the state that is to have the assignment 000. If there is a reset state in the problem, it is reasonable to give it this assignment; if not, the choice is arbitrary. Suppose the combination 000 is assigned to state A; then G must have an adjacent assignment. But each cell in the map has *three* others adjacent to it; which one is chosen for G depends on which other adjacencies are needed. In the present example, G is not required to be adjacent to any other state, so the placement is very flexible. One possibility is to assign 001 to G. The remaining assignments are made using the same approach, resulting in the assignment map in Figure 11c.

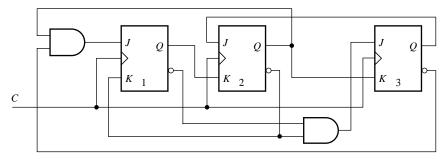

The next step in the design process is to construct transition and output tables. This is done using the assignment map and the given state table. The result is shown in Figure 12a. Let us again assume that JK flip-flops are to be used in the implementation; refer to Figure 7a for the transition requirements for this flip-flop. From Figures 7a and 12a, we construct the J and K excitation maps for each flip-flop. The result for the first flip-flop is shown in Figure 12b. The others are obtained similarly. Expressions for the excitation and output functions are given in Figure 12c

**Exercise 4** Construct the output map and the excitation maps for the other two flip-flops in Example 4 and confirm the expressions given in Figure 12c. ◆

**Exercise 5** In Example 4, suppose that the implementation is to use D flip-flops. Determine the maps for the D excitations and, from these, the state decoder. Compare the hardware with the case that uses JK flip-flops.

### **EXAMPLE 5**

The objective of this example is to find a good assignment scheme for the state table in Figure 13*a*.

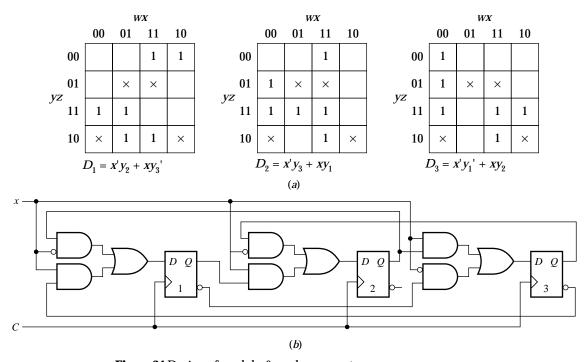

|     |                   | $y_1^+ y_1$ | $y_{2}^{+}y_{3}^{+}$ |       | Z            |          |    | X  | $y_1$                |    |          |    | X  | $y_1$ |          |

|-----|-------------------|-------------|----------------------|-------|--------------|----------|----|----|----------------------|----|----------|----|----|-------|----------|

|     | $y_1 y_2 y_3$     | x = 0       | <i>x</i> = 1         | x = 0 | <i>x</i> = 1 |          | 00 | 01 | 11                   | 10 | _        | 00 | 01 | 11    | 10       |

| A   | 000               | 111         | 111                  | 1     | 0            | 00       | 1  | ×  | ×                    | 1  | 00       | ×  | 1  | 1     | ×        |

| G   | 001               | 111         | 111                  | 0     | 0            |          |    |    |                      |    |          |    |    |       | -        |

|     | 011               | _           | _                    | _     | _            | 01       | 1  | ×  | ×                    | 1  | 01       | ×  | 1  | 1     | ×        |

| C   | 010               | 100         | 101                  | 1     | 0            | $y_2y_3$ |    |    |                      |    | $y_2y_3$ |    |    |       | $\vdash$ |

| E   | 100               | 001         | 000                  | 0     | 0            | 11       | ×  | ×  | ×                    | ×  | 11       | ×  | 1  |       | ×        |

| F   | 101               | 000         | 001                  | 0     | 0            |          | -  |    |                      | -  |          |    |    |       | $\Box$   |

| В   | 111               | 010         | 110                  | 0     | 1            | 10       | I  | ×  | ×                    | l  | 10       | ×  |    |       | ×        |

| D   | D 110 101 100 0 1 |             |                      |       | $J_1 =$      | 1        |    |    | $K_1 = y_2' + x'y_3$ |    |          |    |    |       |          |

| (a) |                   |             |                      | (b)   |              |          |    |    | <i>J</i> Z           | 23 |          |    |    |       |          |

$$J_{2} = y_{1}'$$

$$K_{2} = y_{3}'$$

$$J_{3}' = (x' + y_{1}')(x + y_{1} + y_{2}')$$

$$K_{3} = (x + y_{1})(x' + y_{3}')$$

$$Z = x'y_{1}'y_{3}' + xy_{1}y_{2}$$

(c)

**Figure 12** Transition table and excitation maps.

|        | N          | S,z        | -    |                          |             | J | ⁄ <sub>1</sub> |          | y | <b>1</b> |

|--------|------------|------------|------|--------------------------|-------------|---|----------------|----------|---|----------|

| PS     | x = 0      | x = 1      |      |                          |             | 0 | 1              | ,        | 0 | 1        |

| A      | B,0        | B,1        | Rule | Adjacencies              | 00          | Α | С              | 00       | Α | G        |

| B<br>C | F,0<br>E,1 | D,1<br>G,1 | 1c   | AG, BF, CE               | 01          | G | Е              | 01       | F | D        |

| D<br>E | A,0<br>D,1 | C,0<br>G,0 | 2    | AC, AF, BC<br>DF, DG, EG | $y_2y_3$ 11 | D | В              | $y_2y_3$ | В |          |

| F<br>G | F,0<br>C,1 | A,0<br>B,0 | 3    | AB, AC, BC<br>CE, CG, EG | 10          | F |                | 10       | С | Е        |

|        | (a)        |            |      | ( <i>b</i> )             |             |   |                | (c)      |   |          |

Figure 13 State table, required adjacencies, and assignment maps for Example 5.

The first step is to determine the adjacencies using the adjacency rules; they are listed in Figure 13b (verify, please). With seven states, the number of state variables needed is three. Each cell in a three-variable map is adjacent to three other cells, so each state can be adjacent, at most, to three other states. In a full three-variable map, a total of 12 adjacencies are thus available. (Confirm this.) There are only seven states in this example; it turns out that the maximum number of adjacencies present is nine. From the list of required adjacencies, it is clear that A is required to be adjacent to four other states: G, C, F, and B. Since the lowest-priority adjacency is AB, \_\_\_\_ Even

- 1. State table: Given the specifications of a problem in natural language, construct a state table satisfying the specifications, perhaps by first constructing a state diagram.

- 2. Equivalent reduced table: Use appropriate procedures to determine equivalent states and to remove redundant states, thus generating an equivalent reduced table. (Procedures will be considered in the following section.)

- 3. *State assignment:* Choose a state assignment.

- 4. Transition and output tables: Use the assignment to construct these.

- 5. Excitation maps: Choose a flip-flop type; using the transition table and the excitation requirements for the chosen flip-flop, construct excitation maps.

- 6. Excitation functions: Derive expressions for these from the maps.

- 7. *Output functions:* Derive expressions for these from the output table.

- 8. *Implementation:* Implement the state decoder from the excitation functions and the output decoder from the output functions.

Figure 14 Design procedure for Mealy machines.

that one should be the first to be abandoned. Similarly, the adjacency CG should be abandoned, since C (and G) cannot be made adjacent to four other states.

Whenever there is a choice, try to achieve those adjacencies at one priority level that are also required at a lower level. Aside from AB and CG (which we abandoned), the remaining adjacencies in rule 3 are also required by higherorder rules.

The number of achievable adjacencies in this example turns out to be nine, equal to the maximum possible. Figure 13c shows two assignment maps; each achieves all nine required adjacencies. Using JK flip-flops, the first one can be implemented with five AND and four OR gates. The second one needs one more OR gate.

**Exercise 6** Carry out implementations for the two assignments given in Example 5 and confirm the stated results. Convert to all NAND gates.

# 3 GENERAL DESIGN PROCEDURE

Each of the elements of a procedure for the design of synchronous sequential machines has been discussed in preceding sections of this chapter. We are now ready to consolidate these elements into a general design procedure. We will illustrate this general procedure by applying it to some specific examples.

# Mealy Machine

The Mealy and Moore circuits are models that were shown in Figure 1. When a sequential circuit design problem is specified in terms of the outputs desired for specific sequences of inputs, no model is generally specified. For a given design requirement, it is conceivable to carry out the design based on either model. That means two different designs (state tables) can be obtained. It also means that one of the designs can be obtained from the other. In this book we will deal with both Mealy and Moore machines. The general design procedure for Mealy machines is given in Figure 14.

Figure 15 State diagram and state table of change-of-level detector.

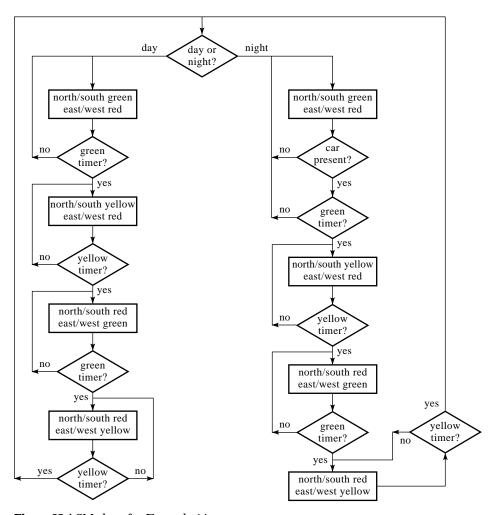

# **EXAMPLE 6**

A sequential circuit is to be designed having a single input line x and a single output line z. Starting in a reset state, the circuit receives input sequences consisting of 3-bit binary words. Each input word follows the preceding word with a delay of one clock period. The circuit must be in the reset state at the beginning of each word. The output is to be z = 1 upon receipt of the third bit of a word if the total number of level changes (from 0 to 1 or from 1 to 0) is odd (101, for example, has two level changes while 001 has only one). Such a circuit is called a *change-of-level detector*.

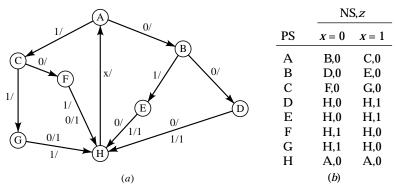

As the first step, we'll obtain the state diagram. Starting from the reset state, no matter what the third bit is, the circuit is to wait one clock period and return to the reset state at the fourth clock pulse. That means the third bit of the input word sends the circuit to a *waiting* state. Figure 15a shows the state diagram. The reset state is A and the waiting state is H. (To confirm this diagram, cover the waiting state and all the lines coming into it and out of it; then describe each of the states reached after 2 bits in terms of the number of level changes. Confirm the output resulting from each input that sends the circuit to the waiting state.) The diagram and the statement of the problem make it clear that each state is unique and there are no redundant states; no two states are equivalent to each other.

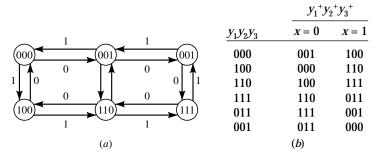

The next step is the state table; this is easily constructed from the state diagram and is shown in Figure 15b. (Confirm this, please.) Since each state is unique, the state table cannot be further reduced. The number of flip-flops needed is  $\lceil \log_2 8 \rceil$  = 3. The rules of thumb for adjacency, shown in Figure 16a, lead to the adjacency map in Figure 16*b*.

For variety, this time let's use D flip-flops, for which the present excitation is the same as the next state. Hence, the entries in the transition table also specify the Dexcitations, so logic maps for the D's can be constructed directly from the transition tables. Likewise for the output. We will supply the results here, but we expect you to confirm all this in an exercise. The following expressions result from the maps.

$$D_1 = y_2 + xy_1' + y_1'y_3$$

$D_2 = y_2'y_3$  \_\_\_\_ Short  $D_3 = y_1'y_2'y_3' + xy_2'y_3$   $Z = x'y_1 + xy_1y_2$  \_\_\_ Even

|         |                     |          |   |            | $y_1^+ y_2^+ y_3^+$ |       |              |  | Z     |              |  |

|---------|---------------------|----------|---|------------|---------------------|-------|--------------|--|-------|--------------|--|

|         |                     |          | J | 1          | $y_1y_2y_3$         | x = 0 | <i>x</i> = 1 |  | x = 0 | <i>x</i> = 1 |  |

| Rule    | Adjacencies         |          | 0 |            | $A \rightarrow 000$ | 001   | 101          |  | 0     | 0            |  |

| 1.0     | DE DE DC            | 00       | A | H          | $B \rightarrow 001$ | 110   | 111          |  | 0     | 0            |  |

| 1a      | DE, DF, DG          |          | _ |            | $G \rightarrow 011$ | 100   | 100          |  | 1     | 0            |  |

|         | EF, EG, FG          | 01       | В | C          | $F \rightarrow 010$ | 100   | 100          |  | 1     | 0            |  |

| 2       | FG, BC, DE          | $y_2y_3$ |   |            | $H \rightarrow 100$ | 000   | 000          |  | 0     | 0            |  |

| 3       | DE, FG              | 11       | G | E          | $C \rightarrow 101$ | 010   | 011          |  | 0     | 0            |  |

| Adjacer | ncies not achieved: | 10       | F | D          | $E \rightarrow 111$ | 100   | 100          |  | 0     | 1            |  |

| DG, EF. |                     | 10       | ľ |            | $D \rightarrow 110$ | 100   | 100          |  | 0     | 1            |  |

| (a)     |                     |          | ( | <i>b</i> ) |                     |       | (c)          |  |       |              |  |

**Figure 16** Adjacency rules, assignment map, and transition table for the change-of-level detector.

Figure 17 Implementation of the change-of-level detector.

The resulting circuit is shown in Figure 17.

**Exercise** 7 Using the transition table in Figure 16c, construct excitation and output maps. From these, confirm the preceding expressions for the D excitations and the outputs. Verify the implementation in Figure 12.

# **EXAMPLE 7**

A synchronous sequential machine is to have a single input line and a single output line. The circuit is to receive messages of 5-bit words coded in 2-out-of-5 code. (See Chapter 1 for a description of codes.) The purpose of the circuit is to detect an error in any of the words. Thus, the output is to become 1 whenever a 5-bit word does not represent a valid code word. At the end of each word the machine is to return to the reset state.

Figure 18 State diagram of error detector in 2-out-of-5 code words.

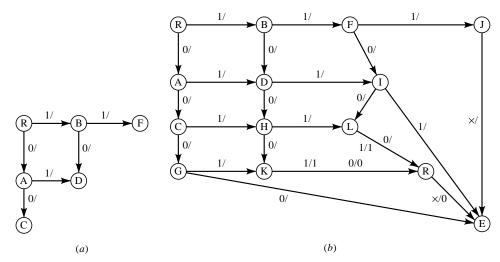

**State Diagram** Let the reset state be labeled R. One possibility for the structure of the state diagram is a tree, starting at state R. In such a diagram, when the machine is in any state, each of the two possible input values leads to a new state. Thus, the state diagram will have  $2^5 = 32$  states. That not all of these are independent states is seen by examining the information that is needed upon receipt of the kth bit:

- How many bits have been received so far?

- How many of these are 1 bits?

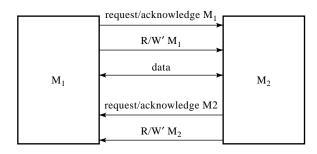

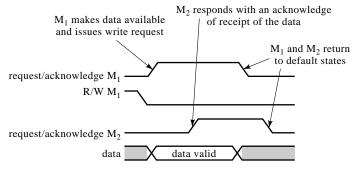

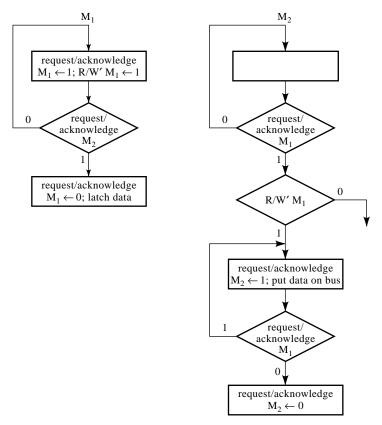

Starting with the reset state, after the receipt of the second bit of a word, there are three possibilities: the number of 1 bits received is 0, 1, or 2. The partial state diagram is shown in Figure 18a. The three possibilities identify just three states after receipt of the second bit. A tree structure would require four states at this point. Upon receipt of the third bit of the word, there are four possibilities for the number of 1 bits received to that point—0, 1, 2, and 3—and thus four new states, labeled G, H, I, J in Figure 18b. Note that no matter what the fourth bit is while at present state J, the received word will never be in 2-out-of-5 code. Hence, from state J, the next state will be an error state (for which the letter E is reserved), but the output will not become 1 until the arrival of the fifth bit, whether a 1 or a 0.

The completed state diagram is shown in Figure 18b; to avoid clutter in the diagram, with lines running back to R from each of the states reached after 4 bits, a second copy of R is provided near these latter states. The two copies of R constitute the same state.

**State Table** The next step is to construct the state table from the state diagram. Do this and confirm the table given in Figure 19a.

**Assignment Map** The number of flip-flops needed is  $\lceil \log_2 13 \rceil = 4$ . Apply the rules of thumb for state adjacencies and confirm the list given in Figure 19. An assignment map that achieves all but one of the adjacencies is given in Figure 19b. It is impossible to achieve all three of the adjacencies required by rule 1. Since two of them are \_

Short

|        |            |            | Rule         | A            | djace          | encies           | ;  |                                           | $y_1'y_2'$   | $y_3'y_4'$   |  |

|--------|------------|------------|--------------|--------------|----------------|------------------|----|-------------------------------------------|--------------|--------------|--|

|        |            |            | <br>1a       | E            | K, EI          | L, KL            |    | $y_1 y_2 y_3 y_4$                         | x = 0        | x = 1        |  |

|        | N          | S,z        | 1c<br>2      |              | J, IJ<br>B, CI | D DE             | ,  | $R \rightarrow 0000$                      | 1100         | 1110         |  |

| PS     | x = 0      | x = 1      | ٤            |              | ъ, ст<br>Н, Н  | ,                | ,  | $E \rightarrow 0001$ $K \rightarrow 0011$ | 0000<br>0000 | 0000<br>0000 |  |

| R      | A 0        | D 0        | •            |              | K, El          |                  |    | $R \rightarrow 0011$ $0010$               | XXXX         | XXXX         |  |

| к<br>А | A,0<br>C,0 | B,0<br>D,0 | 3            | E            | K, EI          | Ĺ                |    | $C \rightarrow 0100$                      | 1011         | 1010         |  |

| В      | D,0        | Б,0<br>F,0 |              |              |                |                  |    | $L \rightarrow 0101$                      | 0000         | 0000         |  |

| C      | G,0        | H,0        |              |              | */             | <b>T</b> 7       |    | $F \rightarrow 0111$                      | 1000         | 1001         |  |

| Ď      | H,0        | I,0        |              | 00           |                | $\frac{y_2}{11}$ | 10 | $D \rightarrow 0110$                      | 1010         | 1000         |  |

| E      | R,1        | R,1        |              | _00          | 01             | 11               | 10 | $I \rightarrow 1000$                      | 0101         | 0001         |  |

| F      | I,0        | J,0        | 00           | R            | C              | Α                | I  | J → 1001                                  | 0001         | 0001         |  |

| G      | E,0        | K,0        |              |              | _              |                  | _  | $G \rightarrow 1011$                      | 0001         | 0011         |  |

| Η      | K,0        | L,0        | 01           | E            | L              |                  | J  | H → 1010                                  | 0011         | 0101         |  |

| I      | L,0        | E,0        | $y_{3}y_{4}$ | 17           | E              |                  |    | A → 1100                                  | 0100         | 0110         |  |

| J      | E,0        | E,0        | 11           | K            | F              |                  | G  | 1101                                      | XXXX         | XXXX         |  |

| K      | R,1        | R,0        | 10           |              | D              | В                | Н  | 1111                                      | XXXX         | XXXX         |  |

| L      | R,0        | R,1        | 10           |              |                |                  | 11 | B → 1110                                  | 0110         | 0111         |  |

|        | (a)        |            |              | ( <i>b</i> ) |                |                  |    | (c)                                       |              |              |  |

Figure 19 State table, assignment map, and transition table for example.

Figure 20 Excitation maps for error detector.

Short

Even

required by lower-priority rules, it is these two that are actually achieved. (Confirm everything as you go along.)

**Transition Table** The transition table resulting from the adjacency map is shown in Figure 19c. Since four state variables imply 16 possible states, and there are actually only 13, three of the state variable combinations do not correspond to states of the machine. Hence, we don't care what the next states resulting from such nonexistent present states will be.

**Flip-Flop Type, Excitation and Output Functions** Assume the use of D flip-flops in the implementation. The excitation and output maps require five variables. The excitation maps are shown in Figure 20. Confirm each of these maps and the resulting excitation and output expressions that follow. (The output map is simple enough that it is not shown.)

$$D_{1} = y_{1}'y_{4}' + y_{1}'y_{2}y_{3}$$

$$D_{2} = y_{1}y_{2} + y_{1}'y_{2}'y_{4}' + x'y_{1}y_{3}'y_{4}' + xy_{1}y_{3}y_{4}'$$

$$D_{3} = y_{1}y_{2}y_{3} + x'y_{1}y_{2}'y_{4}' + xy_{1}y_{2} + xy_{1}'y_{3}'y_{4}' + xy_{1}y_{3}y_{4}$$

$$D_{4} = y_{1}y_{2}' + xy_{1}y_{3} + xy_{2}y_{3}y_{4} + xy_{1}'y_{2}y_{3}'y_{4}'$$

$$z = x'y_{1}'y_{2}'y_{4} + xy_{1}'y_{3}'y_{4}$$

### **Moore Machine**

As shown in the model in Figure 1*b*, in a Moore machine the outputs do not depend directly on the inputs. Hence, in the state table of a Moore machine there is a single output column for each present state, independent of the input. An example will illustrate some of the features.

### **EXAMPLE 8**

A synchronous state machine is to be designed to serve as an odd-parity checker. The inputs to be checked for odd parity arrive on an input line x, but the parity is checked only while the signal on another input line y (a synchronizing input) is 1. An output z, depending only on the state, is to become 1 when the parity fails to be odd. A possible sequence of inputs and output are

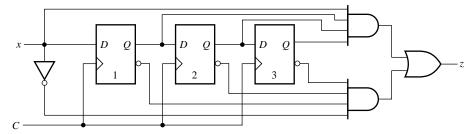

Since the output is to depend only on the state, parity is determined from a memory of just the last two input x bits. This suggests two flip-flops, let's say D flip-flops. A register consisting of two D flip-flops, labeled 1 and 2, is shown in Figure  $21a.^{12}$  Note that, at any given clock tick,  $Q_1$  will have whatever value x had on the preceding clock tick. Similarly,  $Q_2$  will have whatever value  $Q_1$  had at the preceding

<sup>&</sup>lt;sup>12</sup>Registers were introduced in Chapter 5; review if necessary.

Figure 21 Moore circuit realizing Example 8.

clock tick. Using this information, construct three-variable logic maps  $(x, Q_1, and Q_2)$  for  $Q_1^+$  and  $Q_2^+$  and confirm that  $Q_1^+ = x$  and  $Q_2^+ = Q_1$ . Since the output depends only on the state, a logic map for the output will be just a two-variable map  $(Q_1 and Q_2)$ . Draw this map and determine an expression for the output.  $Answer^{13}$

The requirement that the process will proceed only when y = 1 can be met by an AND gate with inputs x and y. The input to the first flip-flop will remain 0 when y = 0, but it will be x when y = 1. The full circuit, including the output decoder, is shown in Figure 21b. (Please verify.)

What was done in this example seems almost like cheating: no state diagram was drawn, no state tables created, no assignments made, and so on. We have seen that two flip-flops will do the trick and that, hence, there is a maximum of four states. As an exercise, construct a state table using the assignments (00, 01, 10, and 11) as state names and construct a separate column for the output, independent of the input. Using this table, confirm the logic maps you previously constructed.

# 4 STATE EQUIVALENCE AND MACHINE MINIMIZATION

Exercise 1 in section 1 (and also Example 7) demonstrated that more than one state diagram (or state table) can be constructed to satisfy the description of a design problem. If one such table has nine states and another has four, the first requires twice as many flip-flops in its implementation as the second. But no

Short \_\_\_\_ Even \_\_\_  $\frac{13z = Q_1Q_2' + Q_1'Q_2}{13z = Q_1Q_2' + Q_1'Q_2} = Q_1 \oplus Q_2$

more information needs to be stored in the first machine than in the second. It must be that whatever task is performed by some of the nine states is performed also by other states, rendering some of the nine states superfluous.

It would be of great benefit to detect these superfluous states and remove them, thus leaving a reduced state table. We have already mentioned the possible reduction in the complexity of the circuit. Once a reduced machine is implemented, what is possibly of even more value is that the reduced complexity makes verification (the experimental determination of faults in a machine) considerably simpler. The purpose of this section is to develop procedures for reducing a given state table to one that carries out the same function with fewer states.

# **Distinguishability and Equivalence**

A finite-state machine operates by receiving a sequence of input symbols, making transitions of state, and emitting output symbols. The input sequence becomes transformed into the output sequence. Look back at the state table in Figure 11 and suppose the circuit is in state B when an input 1 occurs. A transition is made to state D. We describe this by saying that state D *succeeds* state B under an input 1, or that D is the *1-successor* of B. Now suppose that the longer input string 011 arrives when the machine is initially in state A. The final state reached will be E. (Trace out the sequence of states encountered and verify.) So E might be called the 011-successor of A. In general,

If input sequence X is applied to a finite-state machine that is in state  $S_i$  and the machine makes a final transition to  $S_i$ , then  $S_i$  is the X-successor of  $S_i$ .

If the same input sequence X is applied to a machine twice, once when the machine is in state  $S_i$  and once when it is in  $S_j$ , the two output sequences produced may or may not be the same. If they are the same, we will not be able to distinguish the two initial states by means of that particular input sequence. Now suppose that the output sequence is always the same, starting from each of the two states, no matter what input sequence is applied. Clearly, the two states could never be distinguished from each other. This leads to the following definition:

Two states  $S_i$  and  $S_j$  in a finite-state machine are equivalent if the same output sequence is produced in response to an input sequence, starting in either state, and this is true for every finite input sequence.

If the potential equivalence of two states were to be checked using this definition, a whole career would be needed to check all possible input sequences. Clearly, a shorter test is needed. Suppose that, when the machine is started in two different states, the output sequences produced by the same input sequence are *not* the same. The two states can then be distinguished. We make the following statement:

Two states  $S_i$  and  $S_j$  of a machine are distinguishable if and only if there exists at least one finite input sequence that produces different output sequences starting first from state  $S_i$  and then from  $S_j$ . If the distinguishing sequence has length k, then the two states are k-distinguishable.

Short

Even

|    |       |             |   |    | NS           | NS,z         |  |  |  |

|----|-------|-------------|---|----|--------------|--------------|--|--|--|

|    | N     | S, <i>z</i> | - | PS | x = 0        | <i>x</i> = 1 |  |  |  |

| PS | x = 0 | x = 1       | - | A  | B,0          | D,1          |  |  |  |

| A  | B,0   | D,1         |   | В  | C,1          | D,1          |  |  |  |

| В  | C,1   | D,1         |   | C  | <b>E</b> ,0  | A,1          |  |  |  |

| C  | C,0   | A,0         |   | D  | A,0          | C,1          |  |  |  |

| D  | A,0   | C,1         |   | E  | B,0          | D,1          |  |  |  |

|    | (a)   |             |   |    | ( <i>b</i> ) |              |  |  |  |

Figure 22 Example machines.

To illustrate, consider states A and D in the state table given in Figure 22a as initial states. The outputs are the same for either input of length 1 (0 or 1). Hence, states A and D are not 1-distinguishable. Now take an input 00, of length 2. Starting from A, the output is 01, but starting from D, it is 00. Hence, states A and D are 2-distinguishable. This leads to the following definition:

Two states that are not k-distinguishable are k-equivalent.

The previous definition for equivalence can now be expressed as follows:

Two states of a machine are equivalent if they are k-equivalent for all k.

In the preceding discussion we have concentrated on output sequences in response to an input sequence. No attention has been paid to the next states that result along the way. In Figure 22a, for example, we found states A and D to be 1-equivalent; then we tested an input string of length 2. Suppose, instead, that we consider the next states after the first input. The next states are not the same starting from states A and D. Furthermore, it is evident that, using those next states as present states, the same output does not result for each input. Hence, the original states A and D are distinguishable.

Let's pursue this line, using Figure 22*b*, which is almost the same table as the one in Figure 22*a*. Now states A, D, and E are all 1-equivalent. Furthermore, the next states from A and E are the same for each input. Hence, after the first input bit, the transition from each of states A and E will be to the same next state; the outputs thereafter will be exactly the same. Hence, A and E are equivalent.

### **Machine Minimization**

The preceding discussion gives a clue as to how to find the states of a machine that are equivalent to each other. Starting from an input sequence of length 1, we group those states that are 1-equivalent. These states are distinguishable from the others. Next we examine the next states to decide on their distinguishability, and so on. The details of the process are best described with an example.

### **EXAMPLE 9**

A state table is given in Figure 23*a*. The objective is to find all groups of equivalent states and to reduce the table to one having a minimal number of states.

|              | NS,z  |              |                           |                       |           |             |

|--------------|-------|--------------|---------------------------|-----------------------|-----------|-------------|

| PS           | x = 0 | <i>x</i> = 1 |                           |                       |           |             |

| A            | D,1   | G,1          |                           |                       | NS        | S, <i>z</i> |

| В            | C,0   | D,1          |                           | PS                    | x = 0     | x = 1       |

| C            | E,0   | F,1          | $P_1 = \{ADF; BCEG\}$     |                       |           |             |

| D            | F,1   | B,1          | $P_2 = \{ADF; BCE; G\}$   | $A \rightarrow S_1$   | $S_{3},1$ | $S_4,1$     |

| $\mathbf{E}$ | B,0   | F,1          | ~                         | $BCE \rightarrow S_2$ | $S_2,0$   | $S_3$ ,1    |

| F            | D,1   | C,1          | $P_3 = \{A; DF; BCE; G\}$ | $DF \rightarrow S_3$  | $S_{3},1$ | $S_2,1$     |

| G            | A,0   | D,1          | $P_4 = P_3$               | $G \rightarrow S_4$   | $S_1,0$   | $S_3$ ,1    |

|              | (a)   |              | ( <i>b</i> )              |                       | (c)       |             |

Figure 23 Partitioning and machine minimization.

In accordance with the plan, we start by identifying those states that are distinguishable with an input sequence of length 1. We find that the group of states A, D, F have the same output for x = 0; they also have the same output for x = 1. Hence, they are not distinguishable with an input sequence of length 1. Similarly, confirm that the states B, C, E, G are indistinguishable with an input sequence of length 1. But these two groups of states are distinguishable from each other. Thus, the totality of all the states in the table can be *partitioned* into two blocks of states, written as follows:  $P_1 = \{ADF; BCEG\}$ . Within each block, the states are indistinguishable with an input sequence of length 1, but those in one block are distinguishable from those in the other.

Next we examine the successor states from all states in each block, one at a time. If, for each input symbol, the next states from all states in a block are not in the same block but fall in two distinct blocks, then the two sub-blocks are distinguishable. Hence, the original block must be subdivided. Thus, for x = 1, the next states from the block BCEG are DFFD; these are all in the block ADF. However, for x = 0, the next states from the block BCEG are CEBA; all except the next state from state G are in the same block. Hence, block BCEG must be subdivided into two blocks, BCE and G. The resulting partition is  $P_2 = \{ADF; BCE; G\}$ , as shown in Figure 23b; it is a *refined* version of  $P_1$ .

The next states from any one block in partition  $P_2$  were found to be in the same block; hence, these next states will have the same outputs for each input bit. (That's because the outputs were the same, even for the larger blocks in partition  $P_1$ .) These next states in each block are, then, 1-equivalent. Hence, their predecessor states are 2-equivalent.

The process is now repeated with partition  $P_2$ . Again we take each block one at a time and, for each input, examine their next states to see if they fall in the same new block. (Clearly, blocks containing a single state need not be examined.) For each input, the next states from the block BCE fall in the same block. This is also true for x = 0 for block ADF; however, for x = 1, the next states for block ADF are GBC. These next states are not in the same block; hence, a further refinement of  $P_2$  is needed, as shown in Figure 23*b*. The states in each new block are 3-equivalent.

The process must be repeated on the multistate blocks in partition  $P_3$ . Go through the process and confirm that no further refinements of the partition are

needed. The states within each block cannot be distinguished; hence, they are equivalent. This final partition is called the *equivalence partition*. Each of the four blocks in the equivalence partition constitutes a state of the machine to which each of the original states in that block is equivalent. If these states are labeled  $S_p$  a reduced state table can be constructed, as shown in Figure 23c.

The description of this process is far lengthier than the actual effort involved in carrying it out.<sup>14</sup> Note, in this example, that the reduced machine needs just two flip-flops in its implementation, whereas the original table required three.

The subject of this section constitutes the second step in the general design procedure described in the preceding section. As noted earlier, when you initially construct a state table to satisfy the specifications of a design problem, it isn't necessary to spend a lengthy amount of time to ensure that there are no redundant states. Any redundant states introduced earlier can always be removed in the machine minimization step. 15

# 5 MACHINES WITH FINITE MEMORY SPANS<sup>16</sup>

What distinguishes sequential circuits from combinational circuits is memory. The information stored in memory, together with an input sequence, determines an output sequence. But how much past data is it necessary for the machine to remember? Is it necessary for the machine to remember past *inputs only*, or can its future behavior be determined from the present input and a memory of past *outputs*? Or is a memory of both inputs *and* outputs necessary?

We will examine three classes of machines in this section. In the three respective cases, the present output is determined by the present input plus

- **1.** A limited number of the immediately preceding inputs

- **2.** A limited number of the immediately preceding outputs

- **3.** A limited number of the immediately preceding inputs *and outputs*

The machines are all said to have *finite memory spans*.

Not all finite-state machines have this characteristic; a machine with a waiting state, for example, does not. It cannot produce an output while in this state, no matter how long it stays there, even if it receives an acceptable input sequence. Each of the three classes of finite-memory machines will be discussed and implemented in certain specific structures.

<sup>&</sup>lt;sup>14</sup>The process is algorithmic in nature. That means software can be produced to carry it out. Here we will concentrate on the principles.

<sup>&</sup>lt;sup>15</sup>The treatment here has been limited to completely specified machines. Incompletely specified machines require the introduction of several additional concepts that require extensive development. These concepts apply also to asynchronous machines, and they will be treated in Chapter 7. If you skip Chapter 7, you will also be skipping coverage of incompletely specified synchronous machines.

<sup>16</sup>This section can be omitted without penalty in terms of preparation for material that follows.

**Figure 24** Canonic implementation of a finite-input-memory machine.

# **Machines with Finite Input Memory**

One possible formal definition of the machines to be discussed in this section is the following.

A finite-state machine M is said to have finite input memory of memory span (or order) m if the present state of M can be determined uniquely from the preceding m input symbols but no fewer than m.

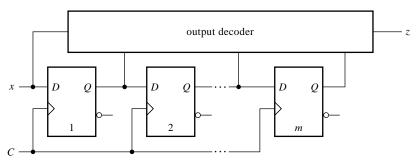

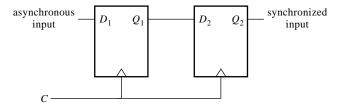

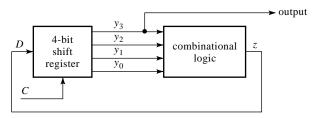

It is clear from the definition that a circuit implementing the memory is an mflip-flop shift register in which the last *m* inputs are stored. The present state consists of the outputs of the m flip-flops in the register. A canonic implementation consists of an m-flip-flop shift register and a combinational output decoder, as shown in Figure 24.

The shift register in Figure 24 is a serial-to-parallel converter. The input information arrives sequentially and is stored in the shift register. When the last bit of an input sequence of appropriate length arrives, both that input and the previously stored information are applied to the combinational logic at the same time, in parallel; the logic of the decoder then produces the desired output.

Since the state of a finite-input-memory machine of span m after an m-bit input sequence is known, the output will become known when the next bit arrives. Hence, such a machine can also be defined as one whose output is determined by the present input and the preceding input sequence of m bits.

The design procedure for a machine with finite memory span can be simplified if the specifications of the design problem allow us to recognize its nature; only the output decoder needs to be designed.

# **EXAMPLE 10**

A synchronous sequential circuit with a single input line x and a single output line z is to be designed so as to produce an output z = 1 whenever an input symbol completes a sequence of 4 identical input bits; the output is to be 0 otherwise.

Just prior to receipt of each input symbol, the machine must remember only the preceding 3 bits. It then produces a 1 or a 0 on the basis of those 3 bits and the present input bit. This, then, is a machine having finite input memory of span 3. Labeling

Short

Figure 25 Canonic implementation of Example 10.

the states Q with subscripts 1, 2, and 3, from left to right, the minterms are 0000 and 1111. Hence, the output is easily written as

$$Z = XQ_1Q_2Q_3 + X'Q_1'Q_2'Q_3'$$

The canonic implementation of the circuit is shown in Figure 25.